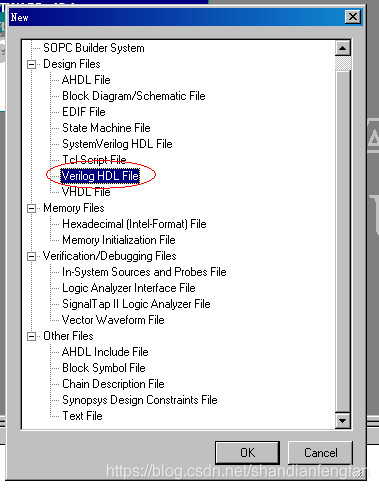

module fenpin(clk_in, //输入信号rst_n, //复位信号 N, //奇数分频倍数3~31 clk_out); //输出信号 input clk_in; input rst_n; input [4:0] N; output clk_out; reg [4:0] cnt, cnt1; reg clk_p, clk_n;always @(posedge clk_in or negedge rst_n)beginif(!rst_n)cnt <= 5’d0;else if(cnt == N-1)cnt <= 5’d0;elsecnt <= cnt + 5’d1;endalways @(negedge clk_in or negedge rst_n)begin if(!rst_n) cnt1 <= 5’d0; else if(cnt1 == N-1) cnt1 <= 5’d0; else cnt1 <= cnt1 + 5’d1;endalways @(posedge clk_in or negedge rst_n)begin if(!rst_n) clk_p <= 5’d1; else if(cnt == ((N-1)>>1)-1) clk_p <= ~clk_p; else if(cnt == N-1) clk_p <= ~clk_p; else clk_p <= clk_p;endalways @(negedge clk_in or negedge rst_n)begin if(!rst_n) clk_n <= 5’d1; else if(cnt1 == ((N-1)>>1)-1) clk_n <= ~clk_n; else if(cnt1 == N-1) clk_n <= ~clk_n; else clk_n <= clk_n;endassign clk_out = clk_p | clk_n;endmodule(7)输入代码之后,要保存文件,点击File—>Save,在弹出的对话框中输入文件名称并保存文件。(8)建立顶层文件,这里我们使用的是图形与代码混合的设计方式,当代码和模块较少时,这种设计方式的优势不能体现出来,但是如果整个工程的模块多了,使用这种设计方式会使得整个设计清晰明了,极大减小出错的概率。选择File—>New,选择文件类型为Block Diagram/Schematic File,点击OK,就生成了一个Block1.bdf的图形文件。(9)往图形文件中添加模块。首先要生成verilog文件的模块。右键点击Quartus II左上角的verilog文件,选择Creat Symbol Files for Current File,就可以生成该文件的模块:(10)生成verilog文件的模块成功之后,就可以在图形文件中添加该模块了。在Block.bdf界面中双击鼠标左键,弹出Symbol对话框,选择选项Project下的模块,点击OK,就会发现选中的模块会跟随鼠标在Block.bdf界面中移动,找一个适当的位置点击左键,把模块放置在该位置。(11)接下来为模块配置输入和输出管脚(请注意此处未配置到芯片的具体管脚)。同样在Block.bdf界面中双击鼠标左键,弹出Symbol对话框,选择pin选项下的input和output管脚,并放置到Block.bdf界面的适当位置,然后开始连线。注意连线的时候,最好把输入输出端口的名称修改为与模块对应的管教一致,而且当模块的某一信号的位宽为多位时,其对应的端口也要修改为多位宽。比如我们分频模块的N输入信号位宽为5,则应把对应的输入端口位宽也修改为5:配置并连接好输入输出管脚之后,整个Block1.bdf界面如下图所示:(12)接下来保存Block1.bdf文件为sanfenpin.bdf文件,然后在左上角的Files下面右键点击sanfenpin.bdf文件,选择Set as Top-Level Entity,把该文件设置为顶层文件。(13)点击工具栏上方的编译按钮,编译整个工程。2. 波形仿真(1)建立波形文件。点击File—>New,选择Vector Waveform File,点击OK,则生成了一个波形文件Waveform1.vwf。(2)往波形文件添加信号。在波形文件的Name窗口单击鼠标右键,选择Insert—>Insert Node or Bus。然后在弹出的Insert Node or Bus对话框中点击Node Finder:在弹出的Node Finder对话框中,在Filter选项中选择Pins:all,再点击List,然后在Nodes Found方框中将显示所有输入输出信号,选择仿真需要的信号,添加到右端的Selected Nodes方框中,最后点击OK完成信号的添加。(3)编辑信号。添加信号完成后,就可以看到波形文件的Name窗口下面列出了之前添加的信号。选中Name窗口下的信号后,工具栏将由灰色变为黑色:分别选中各个信号并对其进行编辑,编辑之后保存波形文件:(4)好了,经过以上步骤就可以对波形进行仿真的,通过设置N值为3~31的奇数,就可以N倍的奇数分频信号。点击工具上方的仿真按钮,开始进行仿真:3分频:5分频:7分频:

(图片来源网络,侵删)

0 评论