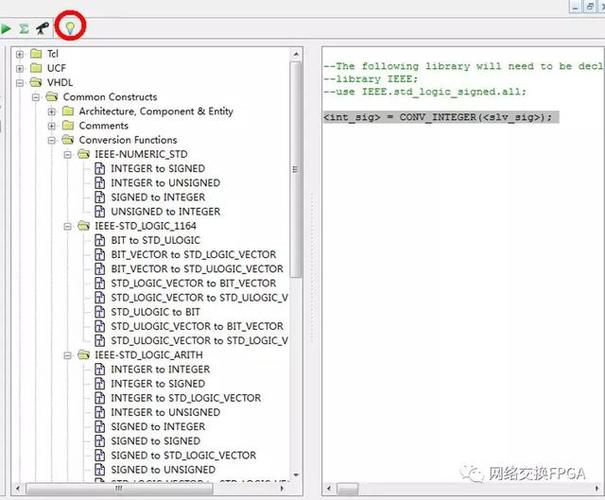

以下仅对Verilog转VHDL过程中出现的问题进行说明。Xhdl软件转换后状态机的问题含有状态机的Verilog代码被xhdl软件转换后会出现两种情况:1、当verilog代码中parameter常量写在紧挨着端口位置时,xhdl软件会将其转换为vhdl中的generic内的可传递的参数,如图:2、当parameter在其它地方出现时,xhdl会将其转换为constant常量,如图:无论哪种方式,将其中有错误的地方改正后,都不会出现状态机运行出错,也就是不用将这种状态机书写方式更改为vhdl语法中专门的状态机书写方式。function转换位置出现问题在用xhdl软件完成转换后会出现function写在了process块内的情况,出现此问题应将function改在architecture下面(与定义信号在相同的位置)。信号只能赋值给与它位宽类型相同的信号如下图中的两个信号:b <= a;在verilog中此种赋值方式意思是将a的前3位赋值给b,但是在vhdl中此种赋值方式会报出位宽不匹配的错误,应将其更改为:b <= a(2 downto 0);同时需要注意a、b的数据类型必须相同,如图中必须都为std_logic_vector类型。没有逻辑与,需用其它办法解决在vhdl中没有逻辑与(verilog中的&&),只有按位与(verilog中的&,vhdl中的and),所以verilog中的逻辑与,在vhdl中有时需要用等价的方式替换,比如:需要替换为:注意数据类型转换符号使用的是否正确在vhdl中有多种数据类型,它们之间可以通过数据类型转换符号相互转换。在xhdl软件中,数据类型转换一般都会出现错误,具体的原因是转换符号使用错误,而在vhdl的语法书上介绍的并不全面。下面介绍几中常用的数据类型转换符号:1、IEEE.std_logic_1164.all库中包含的:(1)bit_vector to std_logic_vector :<slv_sig> = to_stdlogicvector(bv_sig);(2)std_logic_vector to bit_vector :<bv_sig> = to_bitvector(<slv_sig>);2、IEEE.std_logic_arith.all库中包含的:integer to std_logic_vector :<slv_sig> = CONV_STD_LOGIC_VECTOR(<int_sig>,<integer_size>);3、IEEE.std_logic_signed.all库中包含的:std_logic_vector to integer :<int_sig> = CONV_INTEGER(<slv_sig>); 注意:选用某种数据类型转换符号的时候一定要确认是否包含了相应的库。 其它转换符号可以在如下图的ise软件相应的目录下查找if后的判断语句在某些情况会出现语法没错误逻辑出现错误此种情况比较少见,但是一般很难发现,只有通过大量仿真找到错误。具体情况如下图:原verilog代码:if((MDR_port_i & outport) == 32'b0)Xhdl软件转换后语法无错误逻辑出现错误:IF((MDR_port_i /= \"0000000000000000000000000000000\") AND outport /= \"0000000000000000000000000000000\" = false)修改后:IF((MDR_port_i AND outport) = \"0000000000000000000000000000000\" )个人总结:在原verilog代码中,当if后的判断句出现按位与(&)时,Xhdl软件转换成vhdl后很大可能会出现语法正确逻辑错误。并置运算时遇到的问题由于在verilog语法中,位宽不同的两个信号也可以相互赋值,但是在vhdl中对此有严格要求位宽相同,而xhdl软件在转换的时候不会检测这些,所以经常会出现位宽不匹配的情况,尤其是在并置运算时,所以要严格检查并置后的位宽与所赋值信号是否相同。在verilog中某一信号可以赋值给几个并置的信号,但是在vhdl中不允许这么做,除非左侧并置的都为std_logic类型信号,右侧为std_logic_vector类型信号,注意此时在vhdl中并不是用“&”这个并置运算符,而是“,”。(bit以及bit_vector是否有相似功能暂时未知)具体情况如图:错误,因为b是std_logic_vector类型正确情况如下图:Bool类型的运用以及会出现的问题在verilog中几个信号经过关系运算后返回的值是1或者0,但是在vhdl中返回的确是bool类型的值,也就是说返回的是true或者false。1、vhdl中在if后的判断条件最后必须为布尔类型,如图:2、verilog和vhdl中信号经过关系运算后返回值的区别,如图:When-else语句不能用在process块内 软件转换后的when-else语句常常被放在process块内,导致出现问题。因为when-else语句是并行信号赋值语句,它本身就相当于一个进程process,因此不能放在进程体中。进程是不能够嵌套的。位移操作左侧为bit类型,右侧为integer类型Verilog中的位移运算经xhdl软件转换后必出现错误,错误的原因是转换成vhdl代码后位移符号两侧数据类型出错,如图错误情况:修改后的正确格式:位移符号左侧应该是bit类型,所以将std_logic_vector类型的信号转换为bit类型,数字“63”默认为integer类型,位移后的结果仍然为bit类型,所以需要将其装换为std_logic_vector类型,并赋值给相同类型的信号。真双口RAM的IP核的使能信号注意真双口RAM的IP核的使能信号的数据类型,在顶层例化时要注意要只取使能信号第0位的与信号连接的方式。由于真双口RAM在例化后“wea”“web”为std_logic_vector(0 downto 0),所以要取这两个端口的0位与信号连接。while循环在vhdl中不要使用while循环,会出现问题,将while循环换为for循环top层输入输出端口不接信号的情况1、在top层,例化的某个模块输出端口不连信号时,只需要在例化此模块处将此端口删除或注释掉即可,如图:2、当在top层例化的某一模块的输入端口无信号连接时,必须将此端口处连接“U(未初始化)”状态(理论上讲将“U”换为“Z”也可以,但实际上会报出语法错误,在vhdl语法书上说是连接“open”状态,实际测试也会报错),如图:case语句的注意事项在vhdl的case语句的语法中,只有分支将所有条件都覆盖后才可以不使用“when others =>”(相当于verilog的default),但是实际中几乎不可能包括所有情况(因为必须连高阻,不定态等状态都包含进去),所以需要在case语句分支条件增加“when others =>”。对于原verilog代码中default后没有任何表达式的情况,在vhdl中对应的地方写上“null”,如图:组合逻辑转换时遇到的问题当含有“always()”这类组合逻辑的verilog代码经xhdl软件转换后以下两种情况需要注意:1、当是三段式状态机中的“always()”被转换时,注意去除其中的状态常量。2、由于vhdl规定case后的判断条件必须是单一信号,所以当原verilog代码中,case后面的判断条件不是单一信号,而是几个信号的组合时,xhdl软件会将这几个信号的组合用组合逻辑赋给一个新的信号,后将新的信号放在case的判断逻辑处,此时需要注意查看组合逻辑块的触发信号是否包含此新生成的信号,具体如图:仿真时注意时钟的问题(上板不会出现此问题)在使用modelsim对vhdl代码进行仿真时,会出现如图的情况:具体的操作就是对c_o信号打拍,可以发现第一拍没有打上(实际是打上了),该测试程序的原理图如图:C将时钟clk_c_to_b和一个信号c_o传递给b,c_o使用时钟clk生成的,在b内用c给的时钟来给c_o打拍。最后发现仿真之所以会出现上面的情况,主要是因为在模块c内对时钟clk进行了一次处理后赋给b(如在c内部进行了clk_c_to_b <= clk),导致出现了如下的波形情况:如果你在使用VHDL与Verilog转换过程中遇到了上面没有提到的问题,欢迎留言讨论。或者你有更好的办法完成两种语言之间的转换,也请不吝赐教。

全文完。

(图片来源网络,侵删)

0 评论